| 手机版

收藏网站

随着 PD3.1 市场的火热,越来越多的电源厂商开始布局相关电源产品,工程师在开发大功率PD3.1电源时,可通过采用氮化镓驱动芯片替代传统方案,简化PFC电路设计;不仅如此,氮化镓驱动合封芯片也能在AHB拓扑等应用中大展身手,应用前景十分广泛。

近期,成都氮矽科技有限公司推出了两款合封氮化镓芯片 DXC0765S2C 和 DXC1065S2C,将 650V 增强型氮化镓晶体管及其驱动器封装在一个芯片内部,降低了氮化镓快充产品开发门槛,丰富了合封氮化镓电源芯片市场。

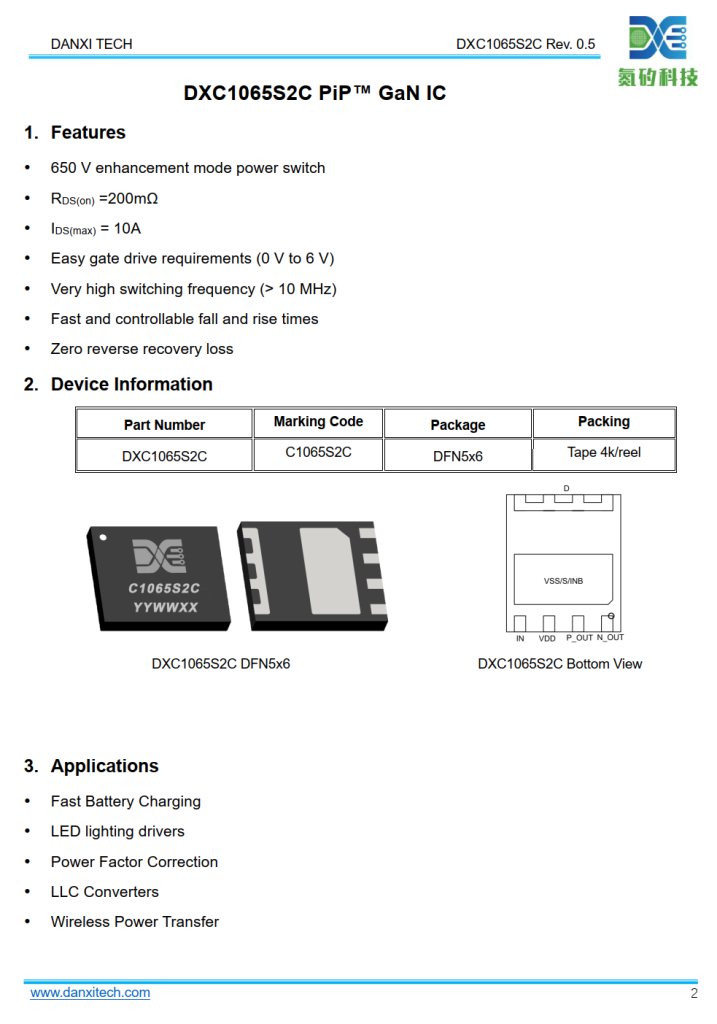

氮矽科技合封氮化镓新品登场氮矽 DXC0765S2C 是一款集成 650V 增强型氮化镓晶体管及驱动器的合封氮化镓芯片,耐压 650V,导阻 400mΩ,最大漏源极电流 7A,单极正电压门极驱动电压 0V~6V,支持3.3V和5V控制信号,开关速度超10MHz,具有零反向恢复损耗。

氮矽 DXC1065S2C 导阻 200mΩ,最大漏源极电流 10A,其余主要参数与 DXC0765S2C 相同;DXC1065S2C和 DXC0765S2C 可应用在快充电源、LED照明驱动器、PFC电路、LLC转换器、无线电力传输等领域。

氮矽合封氮化镓产品采用与单GaN管相同的 DFN5x6 封装,具备很强的通用性,相比传统分离驱动方案,可节省约40%占板面积;此外,采用合封氮化镓芯片可有效减少驱动回路走线,降低寄生参数,应用极限频率更高。

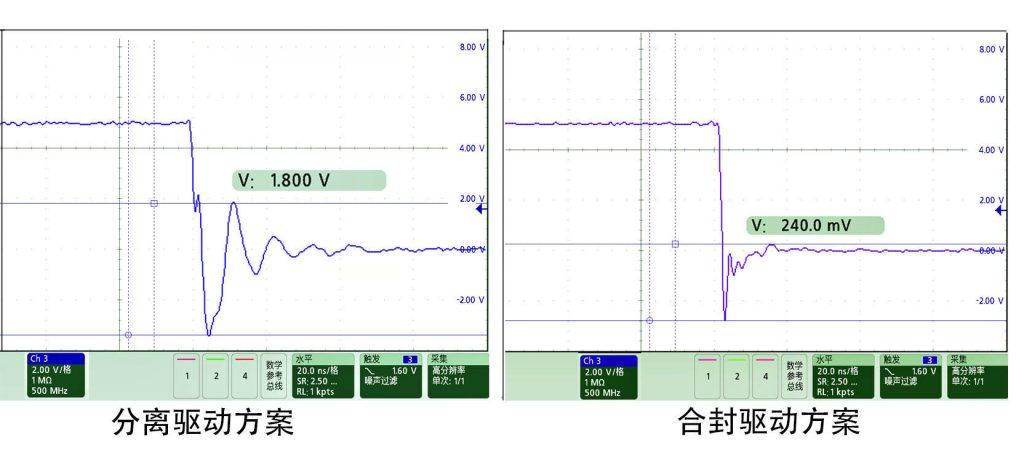

上图为分离驱动方案与合封驱动方案的驱动振铃电压测试图,在下拉电阻同为0Ω的情况下,实测分离驱动方案的驱动振铃电压为1.8V,而合封驱动方案的驱动振铃电压仅仅只有0.24V。增强型氮化镓晶体管的阈值电压一般为1~2V,如果应用工程师选择增加下拉电阻的阻值来防止功率管的误开启,那么势必会影响管子的关断速度,导致应用频率受到限制。

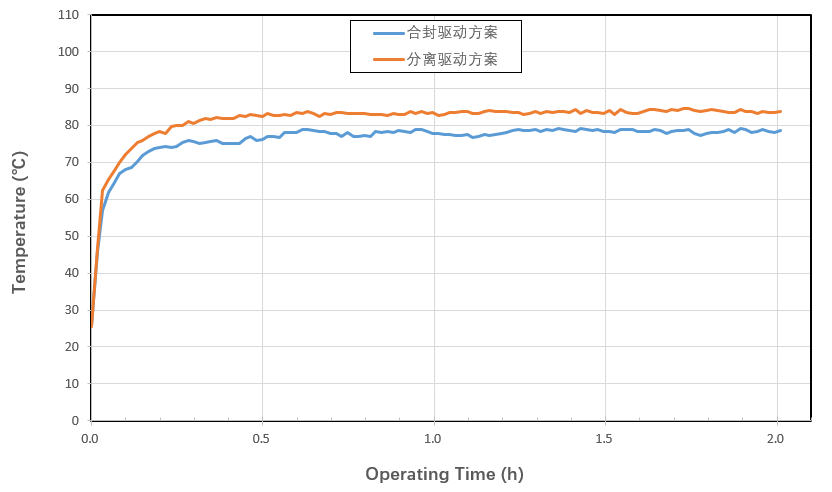

上图为分离驱动方案与合封驱动方案的温升测试图,由于省去了下拉电阻,所以其驱动损耗也低于分离驱动方案,同样的应用条件下,合封驱动方案温度更低,效率更高。

充电头网总结氮矽科技推出的两款合封氮化镓芯片 DXC0765S2C 和 DXC1065S2C,采用 DFN5x6 封装,导通电阻分别为 400mΩ 和 200mΩ。通过将 650V 增强型氮化镓晶体管及其驱动器封装在一个芯片内部,既能够提升整体方案的性能,同时也能减少PCB板的占用,缩小尺寸并减少BOM成本。

氮矽科技2019年成立于成都高新区,2020年初推出氮化镓专用驱动器,填补国内空白,同年底量产多款650V氮化镓晶体管,包括全球最小650V氮化镓器件。截止2022年,氮矽科技已量产各种封装类型的650V/80-400mΩ氮化镓功率器件,以及80-200V氮化镓半桥驱动器、超高速,宽范围输出的低侧氮化镓驱动器等。

氮矽科技凭借在氮化镓领域的先发优势,敢于人先,在氮化镓器件设计、产品封装和测试领域先后实现技术突破,使其在功率氮化镓及其驱动领域具备强大的竞争力。

#氮矽科技