| 手机版

收藏网站

下一代功率半导体公司及氮化镓功率芯片行业领导者——Navitas 纳微半导体(纳斯达克股票代码:NVTS),在2022年9月7日率先发布了 GaNSense 半桥氮化镓功率芯片。相比于现有的分立式方案,半桥功率芯片可实现 MHz 级的开关频率,将有效降低系统损耗和复杂度。

纳微 NV624x 芯片的完整版17页应用手册《AN018:新型采用GaNSense 技术的GaNFast 系列半桥功率芯片》目前已在纳微官网上线,各位如果想要了解关于纳微 NV624x 芯片的更多细节,可前往纳微官网查阅。

这份应用手册详细介绍了 IC 特性和功能、原理图和 PCB 布局指南、电路示例和波形以及热管理说明。还包括电气模型仿真结果,以帮助设计人员快速进行设计。

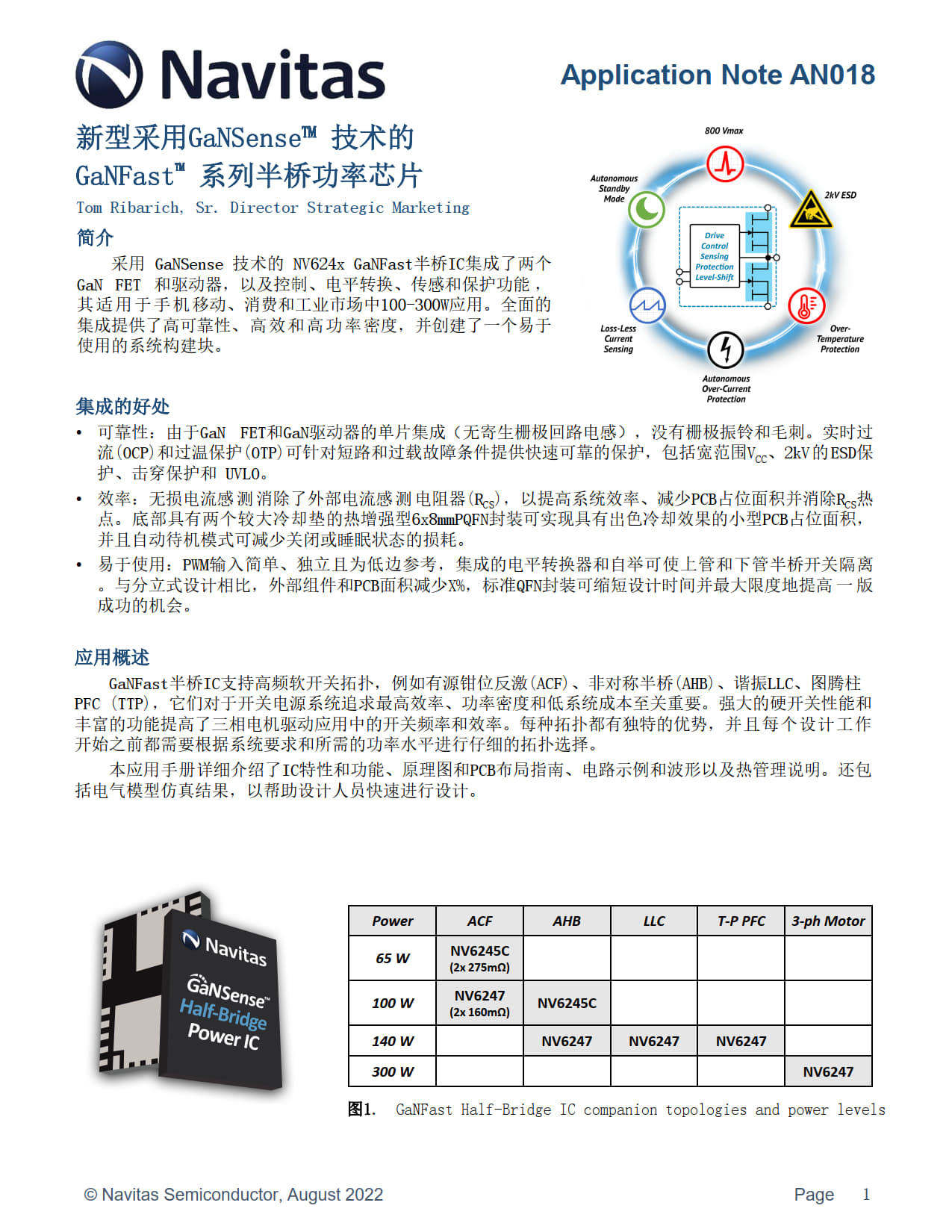

纳微 NV624x 应用手册介绍纳微 GaNFast 半桥 IC 支持高频软开关拓扑,例如有源钳位反激(ACF)、非对称半桥(AHB)、谐振LLC、图腾柱PFC (TTP),它们对于开关电源系统追求最高效率、功率密度和低系统成本至关重要。强大的硬开关性能和丰富的功能提高了三相电机驱动应用中的开关频率和效率。每种拓扑都有独特的优势,并且每个设计工作开始之前都需要根据系统要求和所需的功率水平进行仔细的拓扑选择。

采用 GaNSense 技术的 NV624x GaNFast 半桥 IC 集成了两个 GaN FET 和驱动器,以及控制、电平转换、传感和保护功能 ,其适用于手机移动、消费和工业市场中 100~300W 应用。全面的集成提供了高可靠性、高效和高功率密度,并创建了一个易于使用的系统构建块。

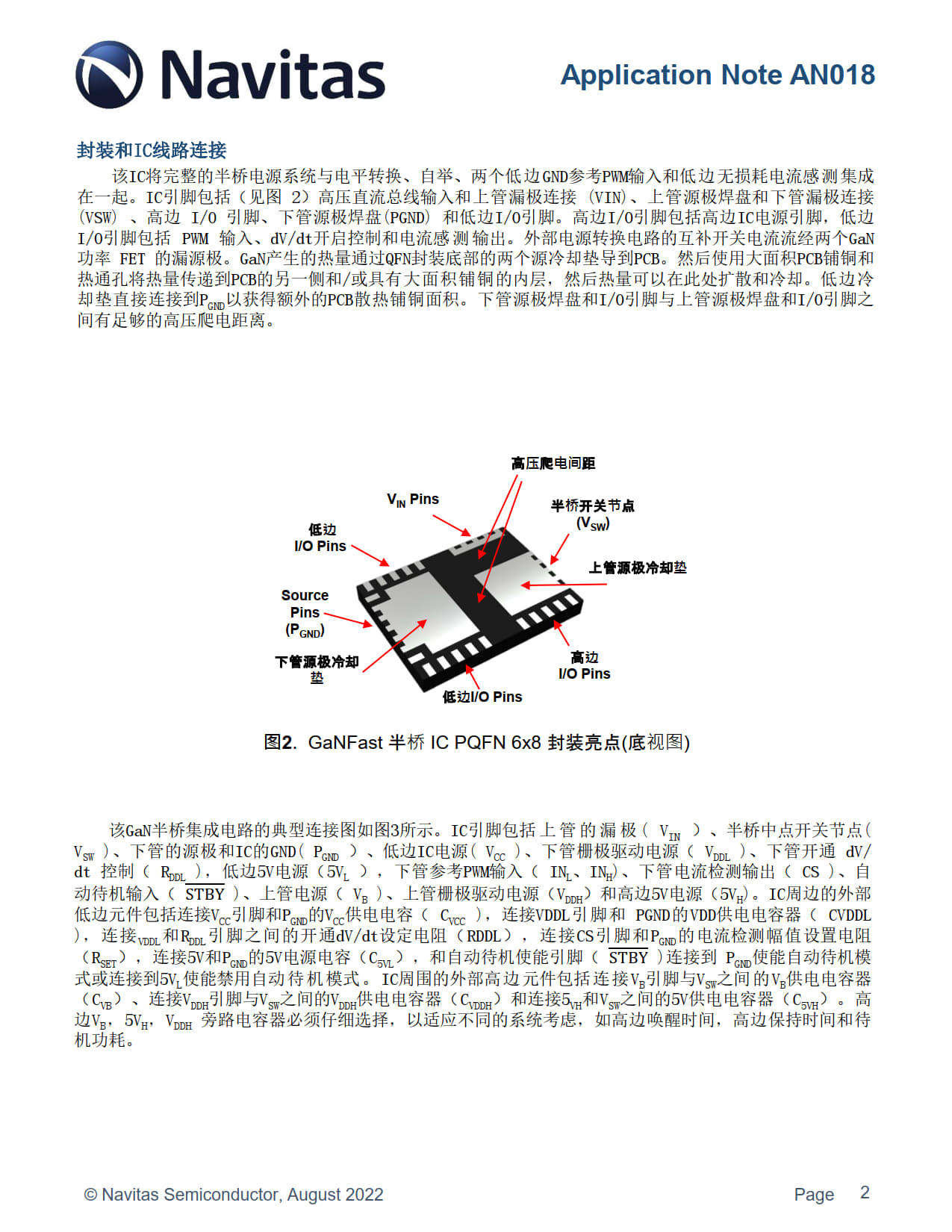

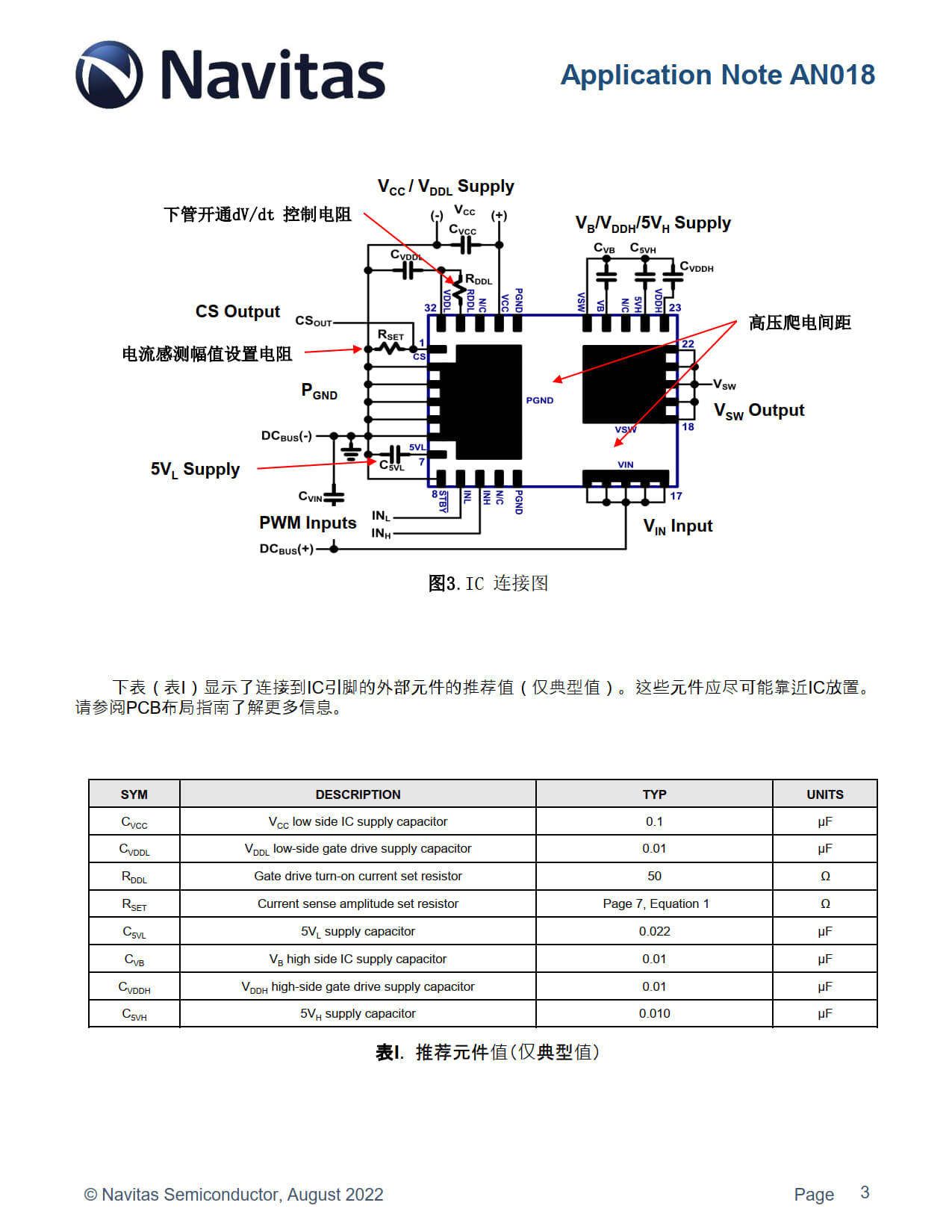

纳微 NV624x 将完整的半桥电源系统与电平转换、自举、两个低边 GND 参考 PWM 输入和低边无损耗电流感测集成在一起。IC 引脚包括高压直流总线输入和上管漏极连接 (VIN)、上管源极焊盘和下管漏极连接(VSW) 、高边 I/O 引脚、下管源极焊盘(PGND) 和低边 I/O 引脚。

高边I/O引脚包括高边IC电源引脚,低边 I/O 引脚包括 PWM 输入、dV/dt开启控制和电流感测输出。外部电源转换电路的互补开关电流流经两个 GaN 功率 FET 的漏源极。

GaN 产生的热量通过 QFN 封装底部的两个源冷却垫导到 PCB。然后使用大面积 PCB 铺铜和热通孔将热量传递到 PCB 的另一侧和/或具有大面积铺铜的内层,然后热量可以在此处扩散和冷却。低边冷却垫直接连接到 PGND 以获得额外的PCB散热铺铜面积。下管源极焊盘和 I/O 引脚与上管源极焊盘和 I/O 引脚之间有足够的高压爬电距离。

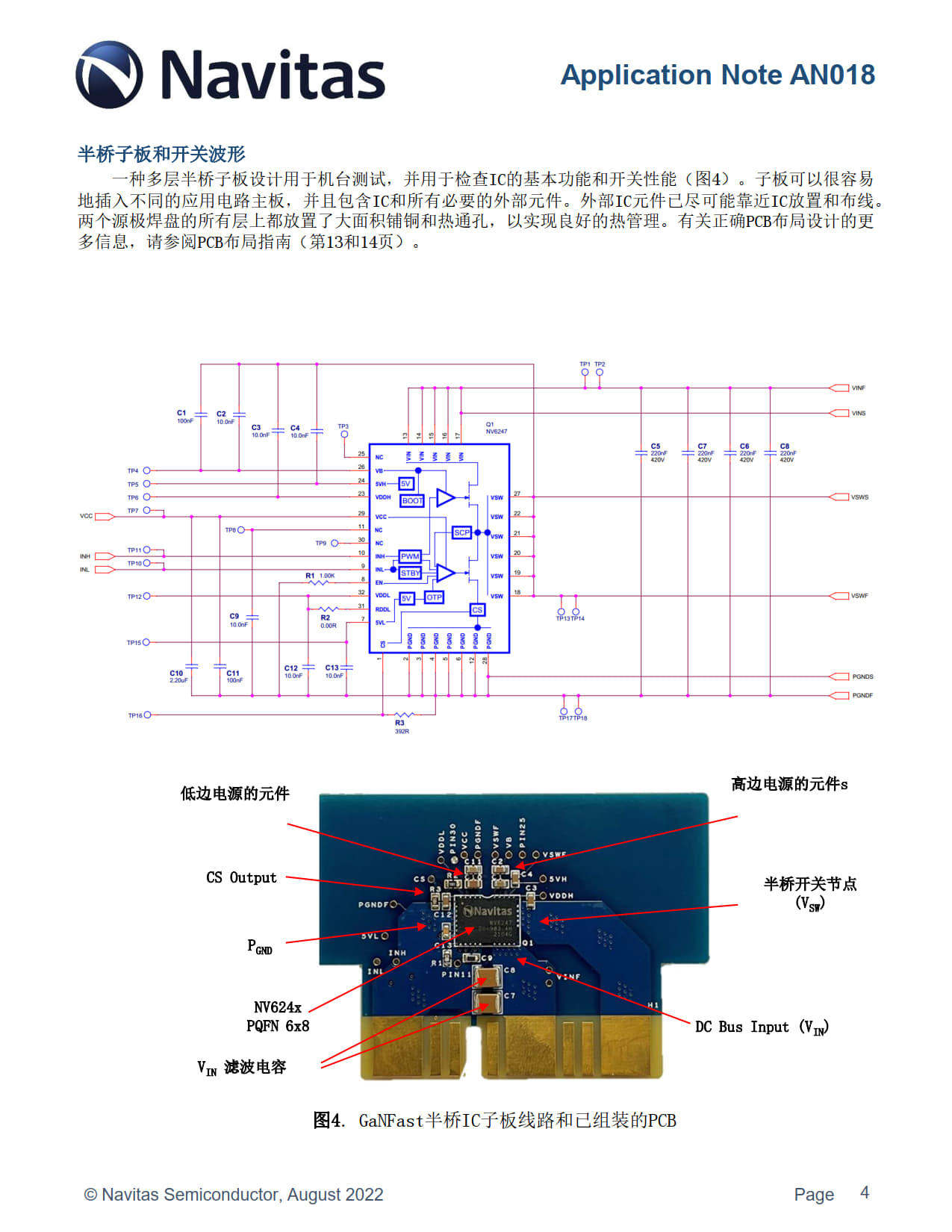

上图展示了一种多层半桥子板设计,用于机台测试,并用于检查IC的基本功能和开关性能。子板可以很容易地插入不同的应用电路主板,并且包含 IC 和所有必要的外部元件。外部 IC 元件已尽可能靠近 IC 放置和布线。两个源极焊盘的所有层上都放置了大面积铺铜和热通孔,以实现良好的热管理。

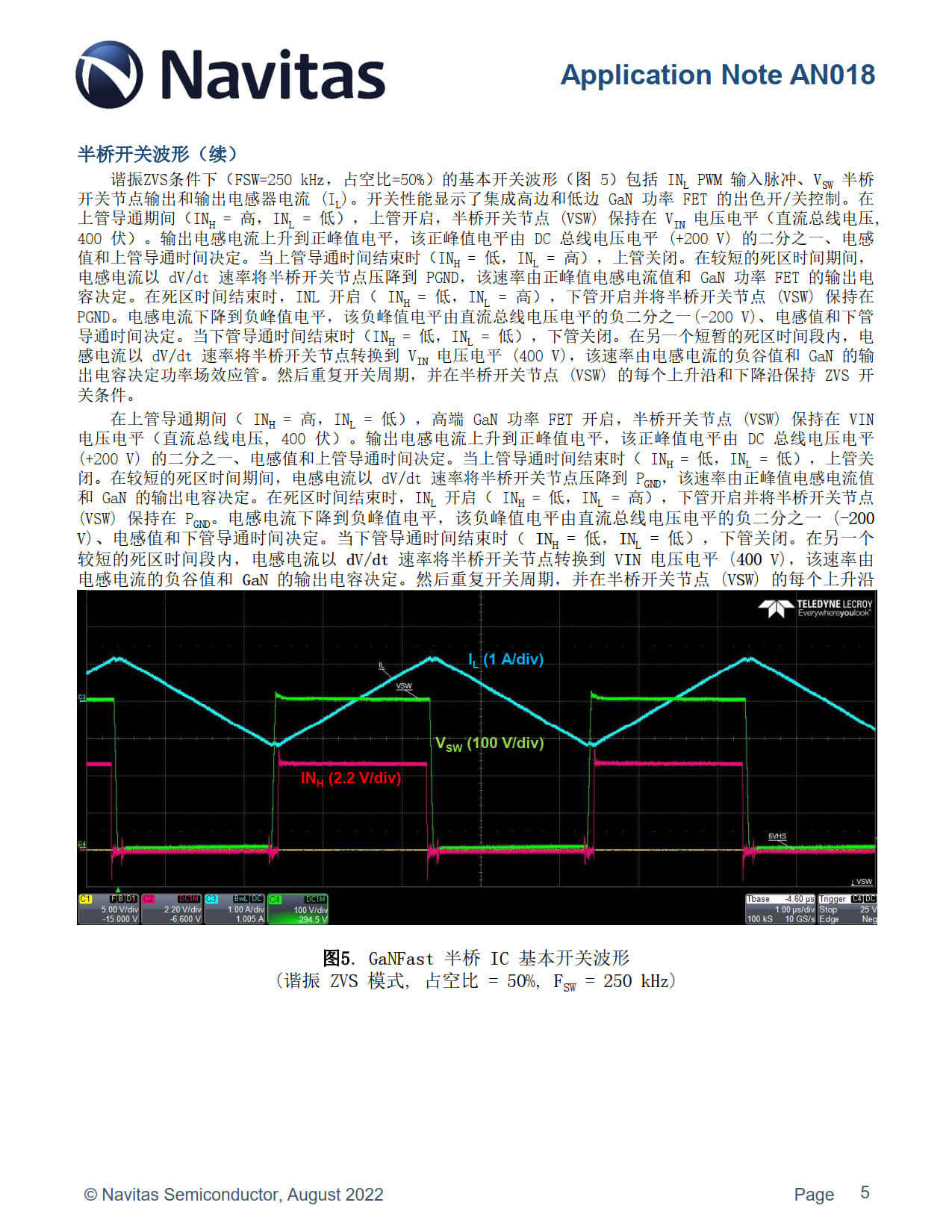

谐振 ZVS 条件下(FSW=250 kHz,占空比=50%)的基本开关波形如上图所示,包括 INL PWM 输入脉冲、VSW 半桥开关节点输出和输出电感器电流 (IL)。开关性能显示了集成高边和低边 GaN 功率 FET 的出色开/关控制。

对于许多应用,有必要检测流经下管的逐周期电流。现有的电流检测解决方案需要在下管的源极连接和 PGND 之间放置一个外部电流检测电阻。使用外部电流检测电阻会增加系统导通损耗,在PCB上产生热点,并降低整体系统效率。

为了消除外部电阻和热点并提高系统效率,纳微 NV624x 集成了精确且可编程的无损电流感测。流经下管的IDS电流在内部被感测,然后被放大、trim 并在电流感测输出引脚 (CS) 处转换为电流。外部电阻 (RSET) 从 CS 引脚连接到 PGND 引脚,用于设置 CS 引脚电压信号的幅度。这允许对 CS引脚信号进行编程,以与具有不同电流感测输入阈值的不同控制器一起工作。

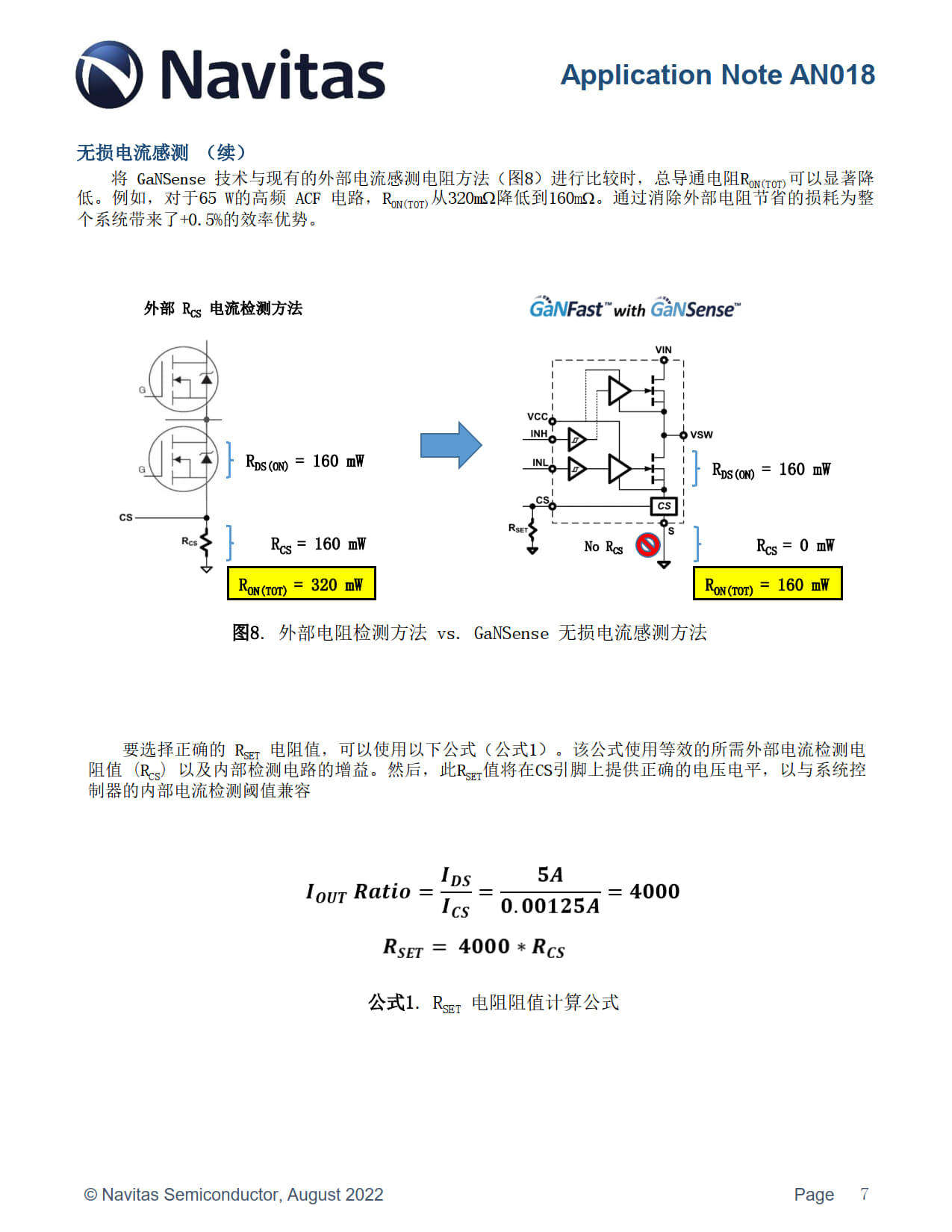

将 GaNSense 技术与现有的外部电流感测电阻方法进行比较时,总导通电阻 RON(TOT) 可以显著降低。例如,对于 65W的高频 ACF 电路,RON(TOT) 从 320mW 降低到 160mW。通过消除外部电阻节省的损耗为整个系统带来了 +0.5% 的效率优势。

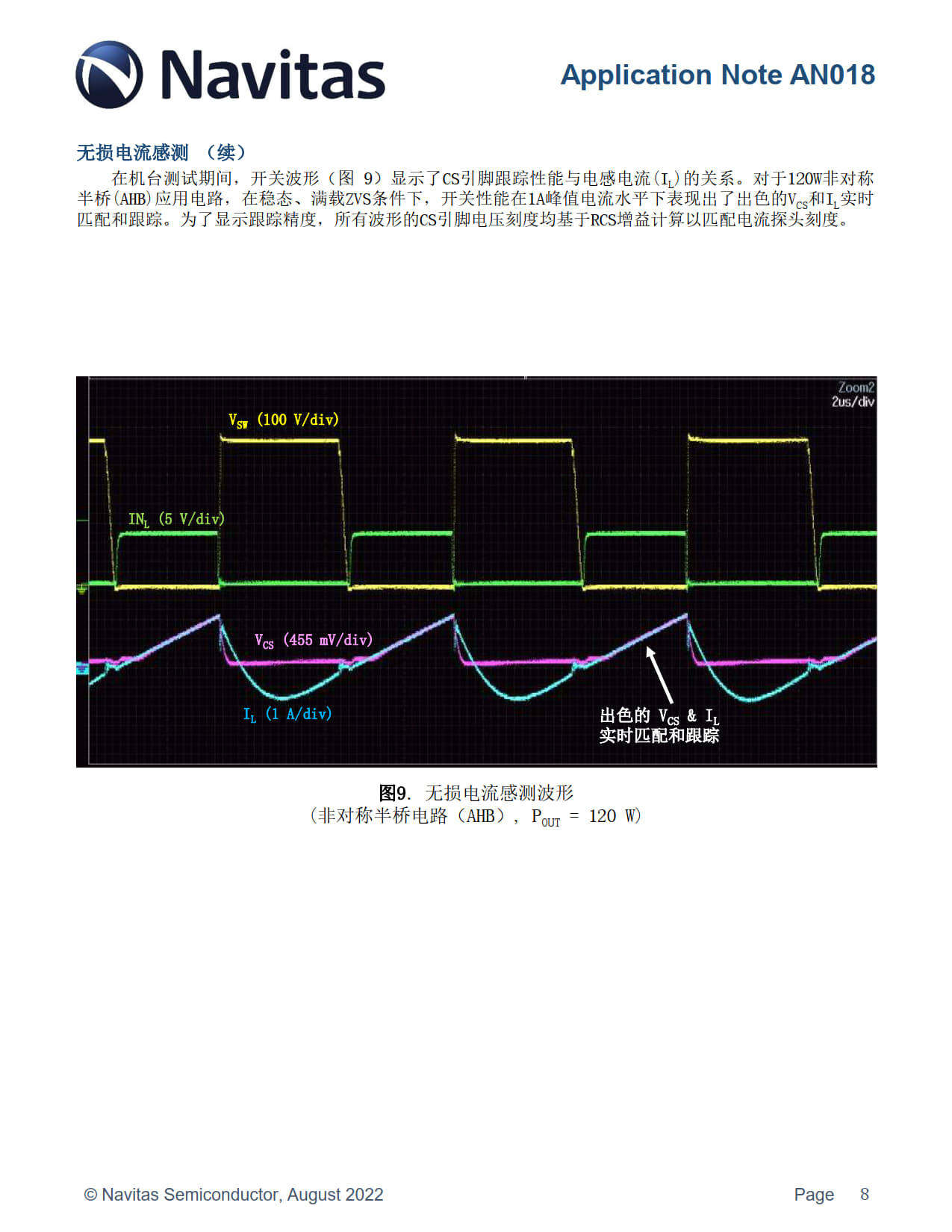

在机台测试期间,上图的开关波形显示了 CS 引脚跟踪性能与电感电流(IL)的关系。对于 120W 非对称半桥(AHB)应用电路,在稳态、满载 ZVS 条件下,开关性能在 1A 峰值电流水平下表现出了出色的 VCS 和 IL 实时匹配和跟踪。为了显示跟踪精度,所有波形的 CS 引脚电压刻度均基于 RCS 增益计算以匹配电流探头刻度。

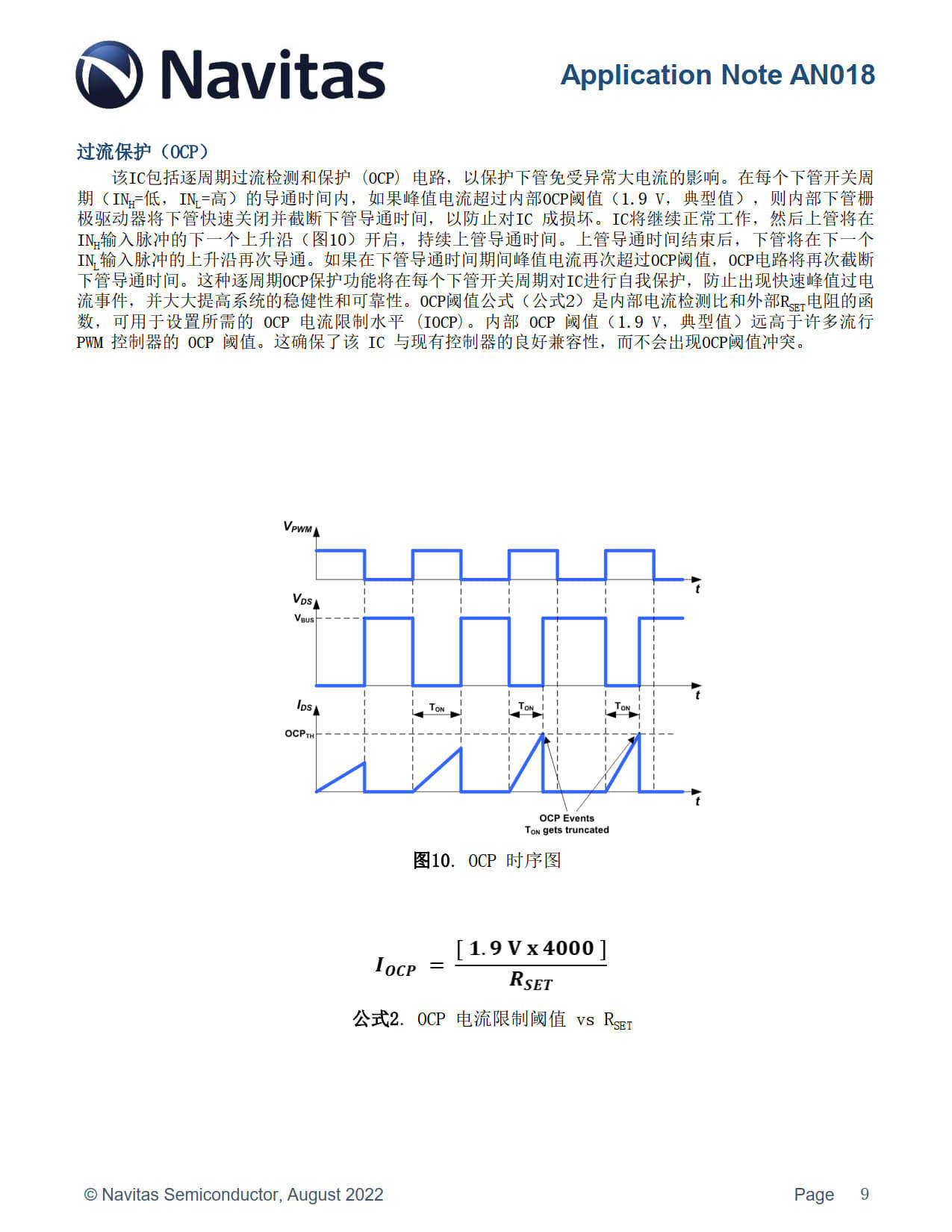

纳微 NV624x 包括逐周期过流检测和保护 (OCP) 电路,以保护下管免受异常大电流的影响。在每个下管开关周期(INH=低,INL=高)的导通时间内,如果峰值电流超过内部 OCP 阈值(1.9 V,典型值),则内部下管栅极驱动器将下管快速关闭并截断下管导通时间,以防止对 IC 成损坏。

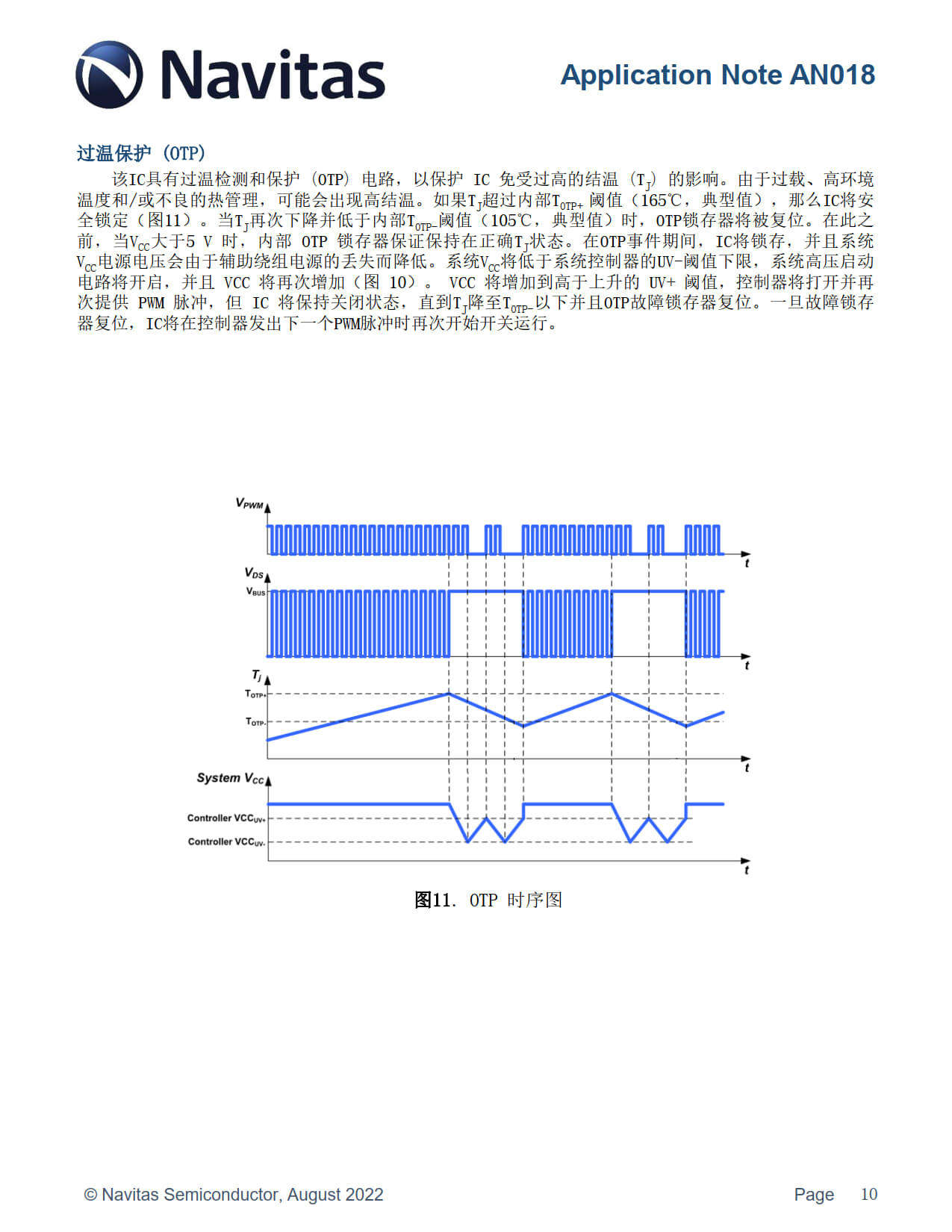

纳微 NV624x 具有过温检测和保护 (OTP) 电路,以保护 IC 免受过高的结温 (TJ) 的影响。由于过载、高环境温度和/或不良的热管理,可能会出现高结温。

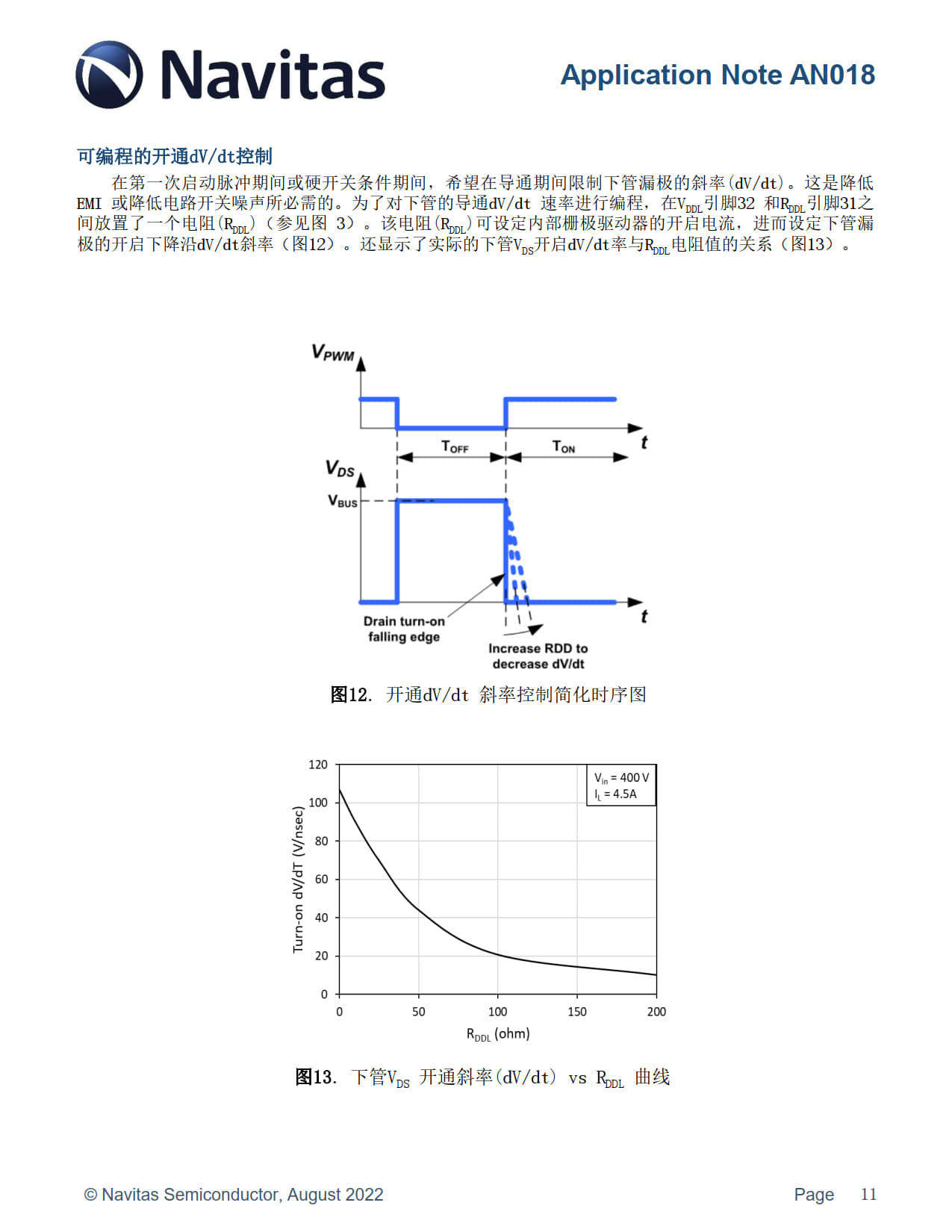

在第一次启动脉冲期间或硬开关条件期间,希望在导通期间限制下管漏极的斜率(dV/dt)。这是降低 EMI 或降低电路开关噪声所必需的。

为了对下管的导通 dV/dt 速率进行编程,在 VDDL 引脚 32 和 RDDL 引脚 31 之间放置了一个电阻(RDDL)。该电阻(RDDL)可设定内部栅极驱动器的开启电流,进而设定下管漏极的开启下降沿 dV/dt 斜率。还显示了实际的下管 VDS 开启 dV/dt 率与 RDDL 电阻值的关系。

纳微 NV624x 具有一种自动低功耗待机模式来禁用IC和降低VCC电流消耗。在正常的工作模式下,PWM脚出PWM信号使氮化镓正常开关。

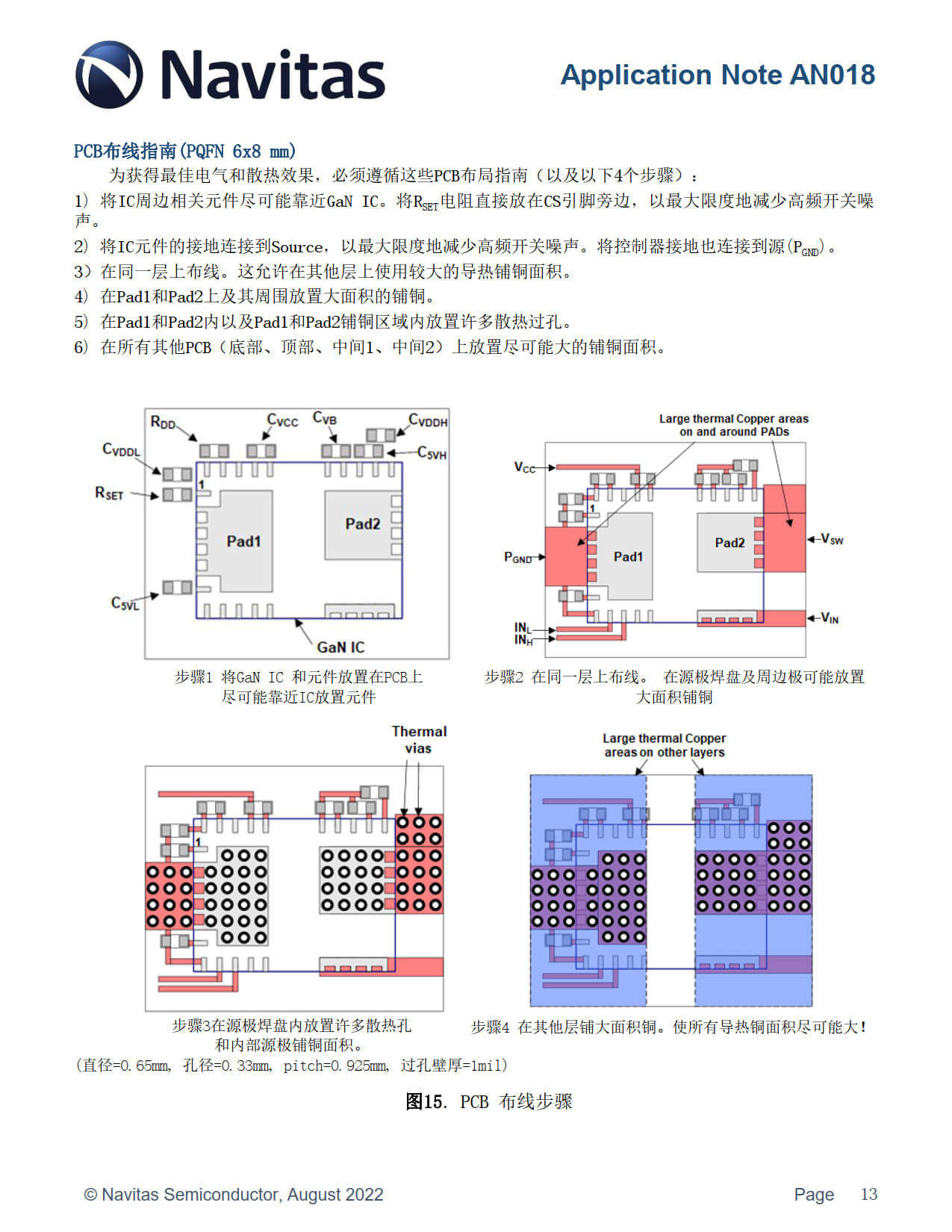

为获得最佳电气和散热效果,必须遵循上图中的 PCB 布局指南。

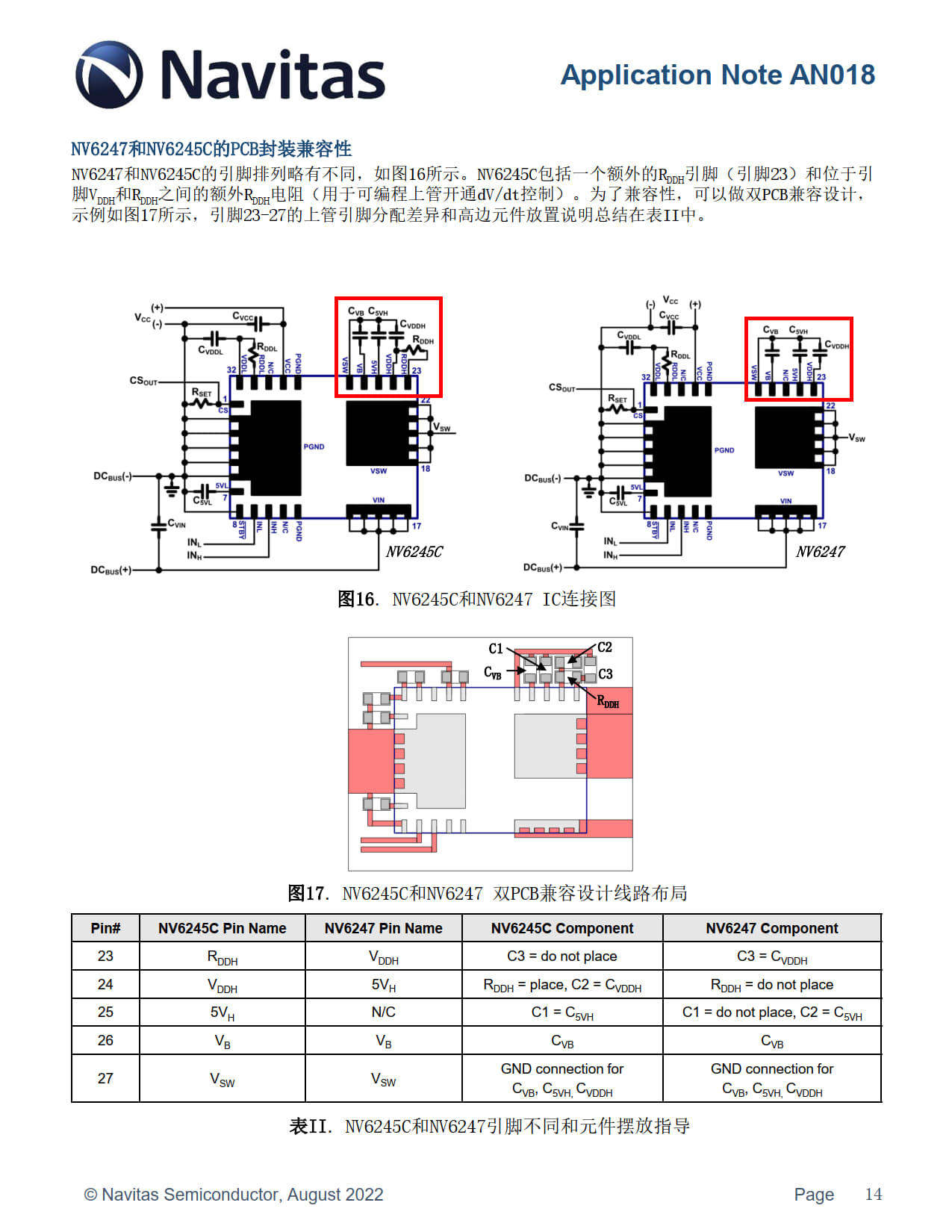

NV6247 和 NV6245C 的引脚排列略有不同,如上图所示。NV6245C 包括一个额外的 RDDH 引脚(引脚23)和位于引脚 VDDH 和 RDDH 之间的额外 RDDH 电阻(用于可编程上管开通dV/dt控制)。

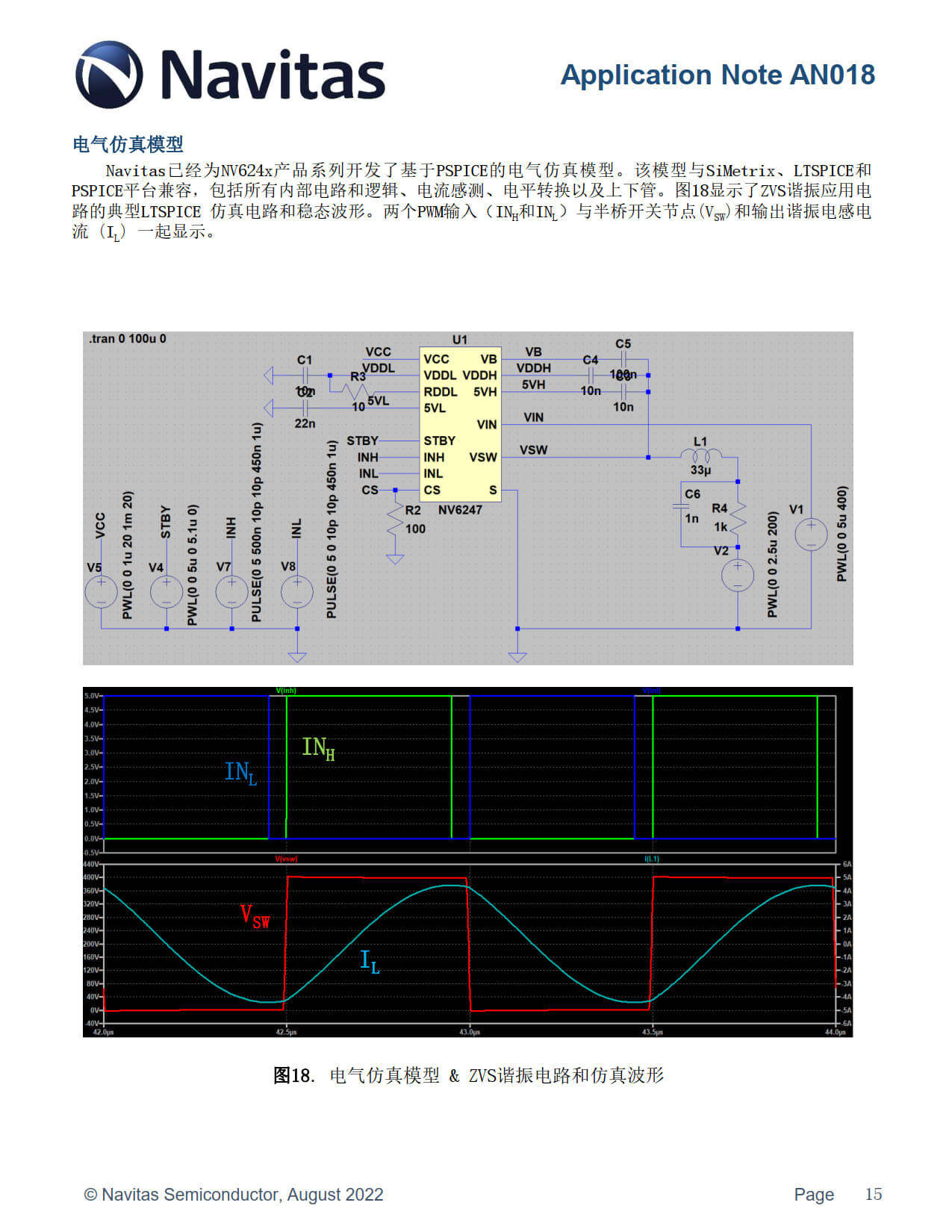

Navitas 纳微已经为 NV624x 产品系列开发了基于 PSPICE 的电气仿真模型。该模型与 SiMetrix、LTSPICE 和 PSPICE 平台兼容,包括所有内部电路和逻辑、电流感测、电平转换以及上下管。

Navitas 纳微已为 NV624x 开发了3D机械模型。NV6247.stp 文件可用并可轻松导入许多流行的 PCB 设计软件平台(如 Altium Designer)。该模型可用于生成组装电源设计的 3D 渲染,以便在发布用于制造的 PCB gerber 文件之前检查任何设计问题。

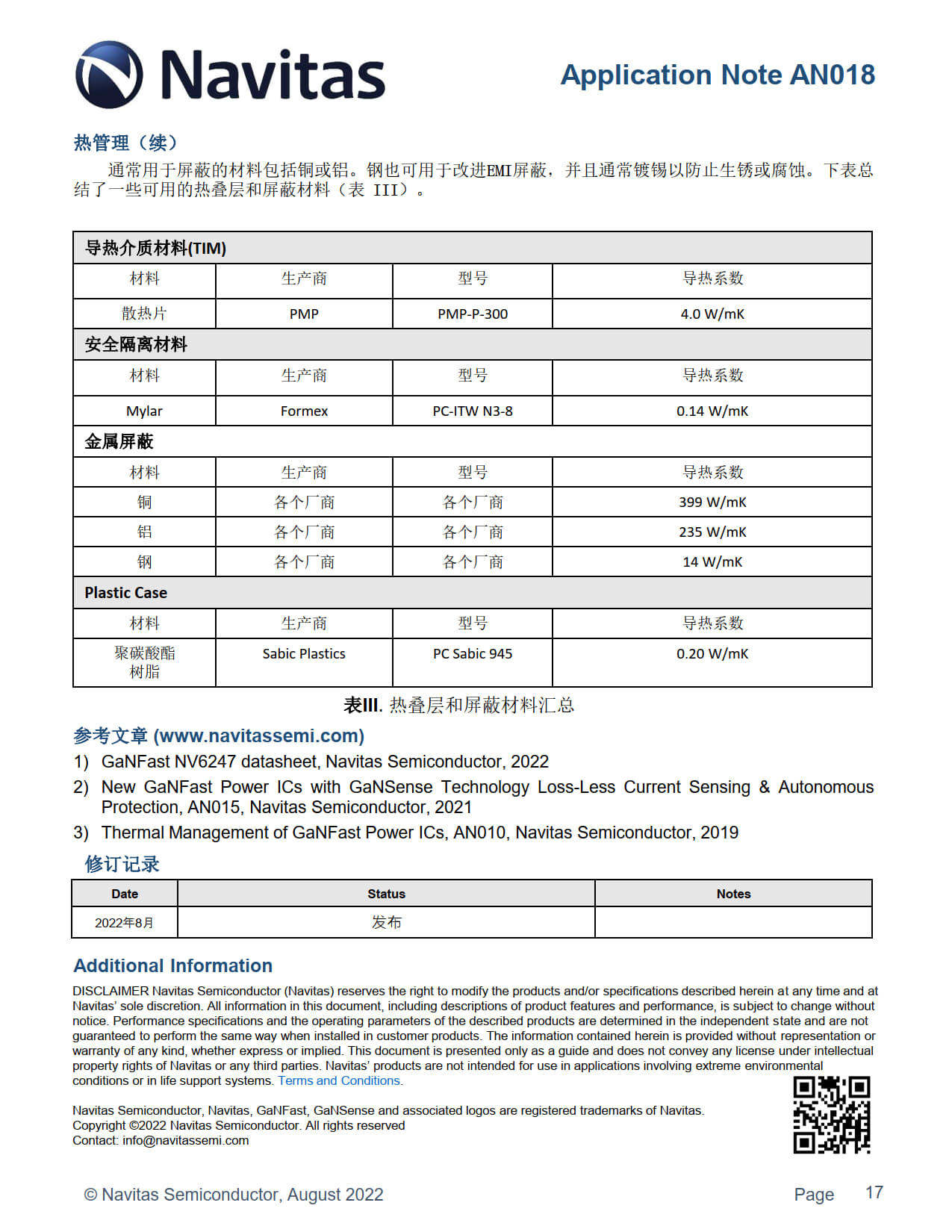

通常用于屏蔽的材料包括铜或铝。钢也可用于改进 EMI 屏蔽,并且通常镀锡以防止生锈或腐蚀。上图总结了一些可用的热叠层和屏蔽材料。

充电头网总结纳微半导体此次发布的采用 GaNSense 技术的 NV624x GaNFast 半桥功率芯片,作为全新一代产品,其集成了两个 GaN FETs 和驱动器,以及控制、电平转换、传感和保护功能 ,可用于手机移动、消费和工业市场中 100~300W 应用场景。

#纳微